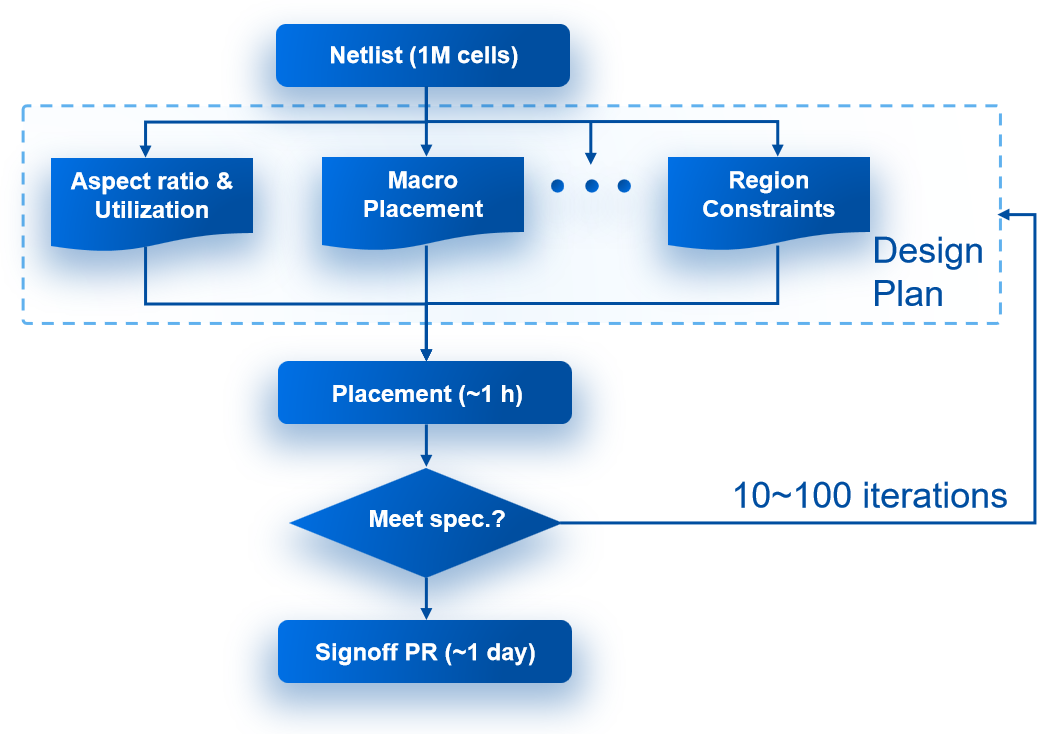

物理设计在数字集成电路的后端设计中扮演着至关重要的角色。它将逻辑综合后的设计,即标准单元和互连的图表示,转化为由逻辑门的物理形状组成的几何表示。随着现代数字集成电路设计规模不断扩大,约束条件日益复杂,设计者通常需要进行反复迭代,寻找具有竞争力的芯片实现方案。

在整个物理设计流程中,布局具有关键的地位。作为设计流程中承上启下的步骤,布局不仅为电路综合提供了重要的指导信息,还决定了整个物理设计在核心PPA(功耗、性能、面积)指标上的表现。实际上,几乎所有后端物理设计中遇到的关键问题都可以在布局阶段得到解决。

▲

图表1 布局在整个集成电路设计流程中占据重要的地位

布局作为一个经典的NP-hard问题,难以最优求解。然而,随着算力需求的增长,数字设计的规模不断扩大,而先进工艺则引入了更加复杂的约束条件和设计规则,使得物理设计的单次迭代时间不断延长,成为了探索设计空间时的最大障碍。

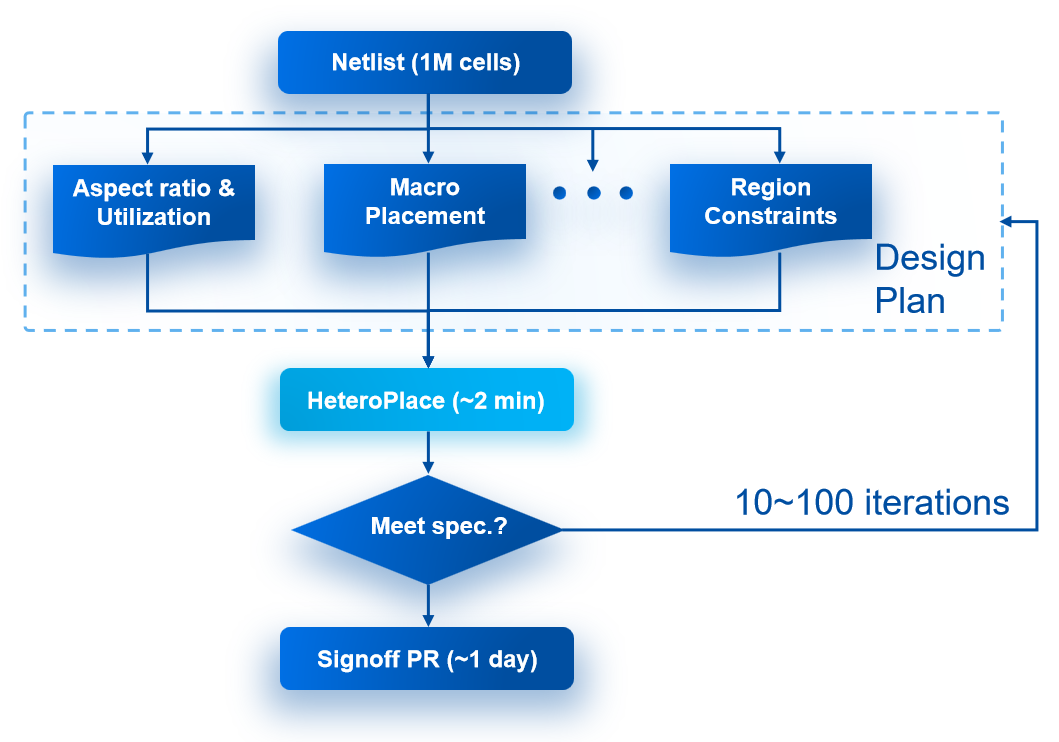

为了应对这一挑战,无锡北京大学电子设计自动化研究院推出基于异构计算加速的快速布局工具HeteroPlace。HeteroPlace基于先进的异构计算架构,支持异构计算的全局布局(global placement)算法,详细布局(detailed

placement)算法,全局布线(global routing)算法和静态时序分析(static

timing analysis)算法,支持时序驱动(timing-driven)以及可布线性驱动(routability-driven)的布局优化算法以获得高质量的布局结果。对比基于多核CPU的传统布局算法,HeteroPlace实现了数倍到数十倍的运行时间加速,可以辅助设计者在芯片研发周期内尝试更多的实现方案,探索更有竞争力的芯片设计。

![]() ▲ 图表2 传统物理设计流程

▲ 图表2 传统物理设计流程

![]() ▲ 图表3 基于HeteroPlace的快速流程

▲ 图表3 基于HeteroPlace的快速流程

HeteroPlace作为一个快速布局工具,既可以帮助后端设计人员快速评估多种实现方案的质量,为最终signoff布局布线流程提供更好的物理规划(如模块物理形状、宏模块位置、区域划分等等),也可以帮助前端设计人员快速评估每种模块架构在最终物理实现的PPA,实现物理感知的前后端融合设计流程,以跨层次的优化方法完成更有竞争力的设计。

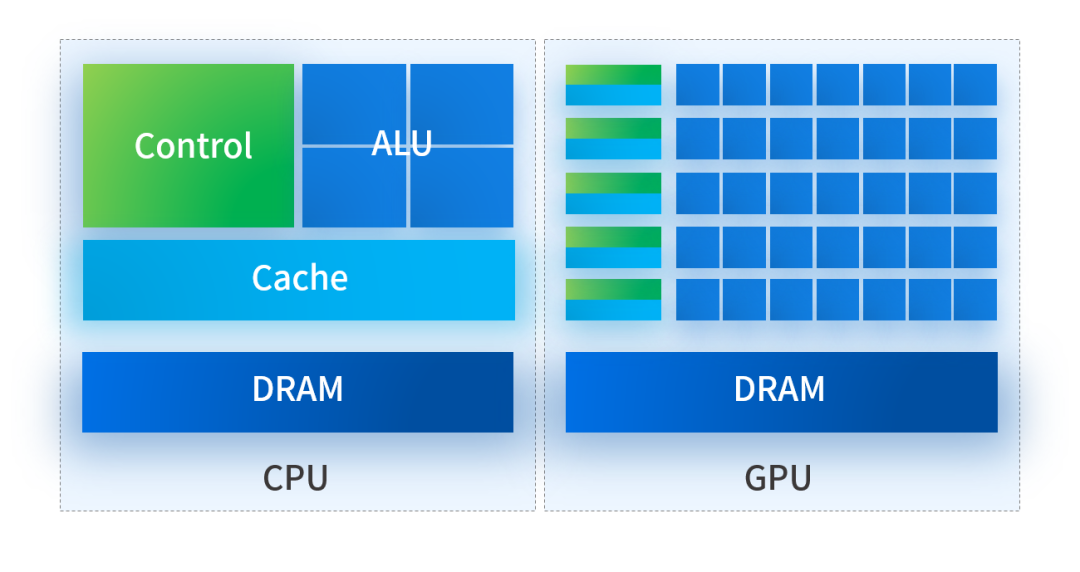

随着科学计算、数据分析、人工智能和图形处理等领域的快速发展,对于更快速、更高能效的计算需求不断增长。传统计算机系统的中央处理单元(CPU)虽然在通用计算任务中表现出色,但对于某些特定应用如数据规整的计算密集型应用,其性能限制越来越明显。

为解决该问题,异构计算将不同类型的处理器整合在一起,让每个处理器处理其擅长的任务。例如,图形处理单元(GPU)在并行计算方面具备卓越性能,可以有效地加速任务中计算密集的部分。近些年来人工智能的突破带来了新的技术革命,也推动了新型处理器的发展,GPU、TPU和FPGA等加速处理器的算力提升速度远远超过CPU。此外,深度学习框架如TensorFlow、PyTorch等的普及也加速了异构计算技术的推广。

![]()

![]()

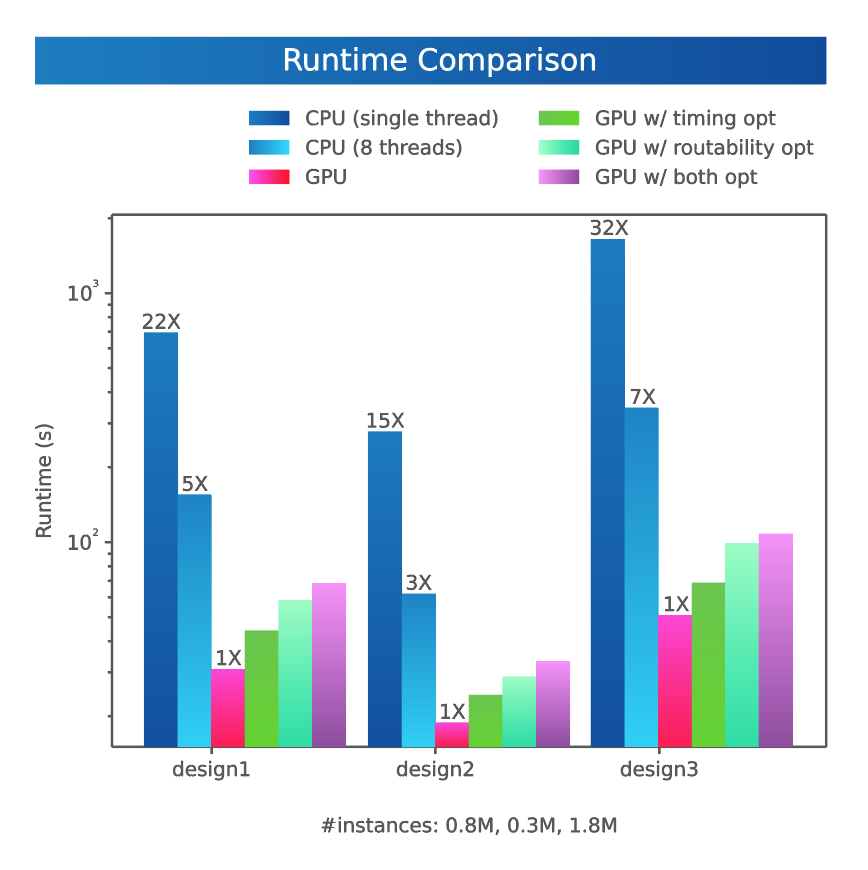

与深度学习的训练相似,EDA物理设计算法同样需要大规模的数据处理和数值求解。HeteroPlace实现了高度优化的异构算子及求解器,利用GPU加速全局布局、详细布局、全局布线和静态时序分析,支持时序驱动以及可布线性驱动的布局优化。

HeteroPlace竞争优势一:

更快速的布局实现

得益于异构计算架构的高并行度和更优化的求解算法,在开源测试案例和实际工业案例上,HeteroPlace可以在约一分钟的时间,完成百万门级模块的基础布局功能(测试服务器为Intel(R) Xeon(R)

Platinum 8358 + NVIDIA A800-SXM4),在两分钟左右的时间完成时序和可布线性优化的布局。相比于单核的CPU模式,异构计算模式可以在运行时间上快15到32倍,且越大的设计加速效果越明显;相比于常见的多核CPU模式(以大部分商业软件支持的8核并行为例),运行时间的加速也有3到7倍。

更快的运行速度使得HeteroPlace可以帮助设计者在有限的设计周期内寻找更优的布局方案,同时也赋予了物理感知的前端设计以更大的可能性。

![]()

HeteroPlace竞争优势二:

更优的布局质量

HeteroPlace内置全局布线器和静态时序分析引擎,可以在布局过程中实时分析当前实现的时序和拥塞程度,并利用高效的优化算法对当前实现方案进行智能化的针对性优化,以此实现更优的布局质量,并显著缩短后阶段详细布线和设计优化的运行时间。

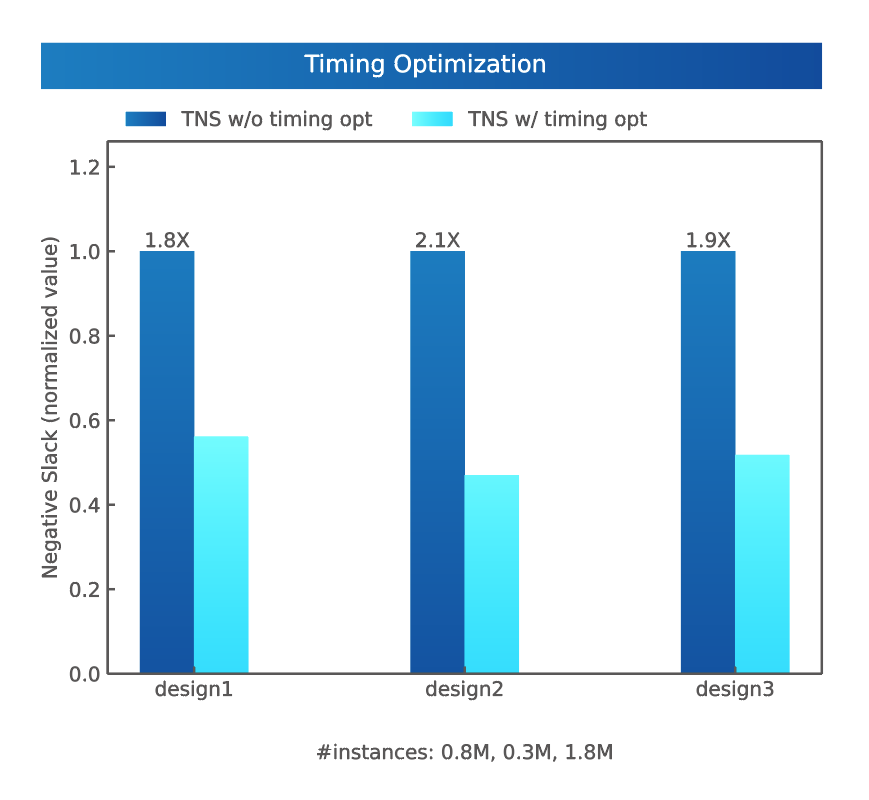

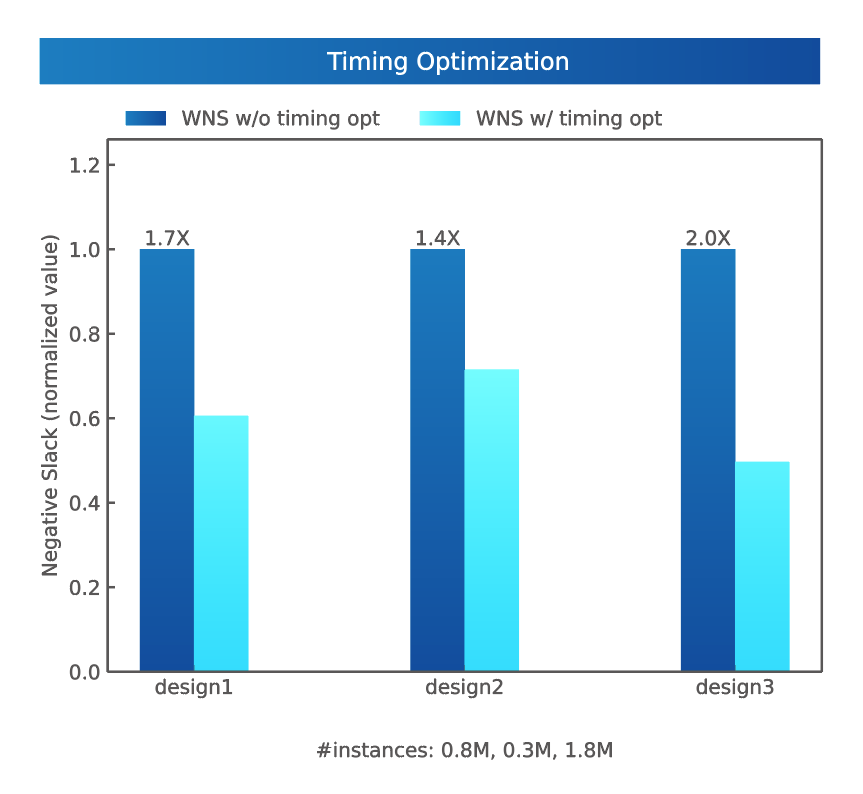

在开源测试案例和实际工业案例上,开启时序优化模式可以减小布局后的TNS 1.8到2.1倍,减小WNS

1.4到2.1倍。可以大大减少物理设计优化阶段Buffer

Tree的数量,优化最终的PPA。

开启可布线性优化后,内置的全局布线器会识别出是否存在严重的hotspot,如果存在严重的hotspot会影响后阶段的实现或最终实现质量,HeteroPlace会利用内置的优化算法优化hotspot附近的单元布局,使得局部的布线资源和布线需求趋于平衡。

![]()

![]()

![]()

HeteroPlace竞争优势三:

更灵活的参数设置

HeteroPlace支持多种分析模式和优化算法,并允许设计者在使用时自定义一些超参数以控制内部的布局流程。对于日益多样化的架构设计,HeteroPlace支持面向设计的自定义布局算法,设计者们可以根据当前设计的特点或者当前设计方法的需求,修改分析算法的约束和优化算法的超参数。(此功能需要联系支持团队)

北京大学EDA研究院深耕物理设计领域多年,积累了多项国际领先的研究成果和国内外发明专利。我们怀着一颗充满热情的心,希望HeteroPlace不仅仅是一个软件产品,而是一个开放的探索框架,与国内杰出的设计者们共同探索更高效的集成电路设计方法。我们将持续不断地提升产品的效率和结果质量,并为您推出更多令人期待的产品和新特性,包括:

混合尺寸布局(mixed-size

placement)

最后,非常欢迎您与我们联系,深入了解并试用体验HeteroPlace。我们期待与您共同努力,共同推动国产集成电路行业的高质量发展。

heteroplace@pkueda.org.cn